플래시 메모리와 SSD

주기억장치-보조저장장치 간 정보 전송의 필요성

● 시스템 초기화(부팅) 과정에서 OS 프로그램을 주기억장치로 적재

● 응용 프로그램이 처음 수행될 때는 디스크로부터 주기억장치로 적재

● 새로이 생성되거나 수정된 데이터는 보조저장장치에 영구 저장

● 주기억장치 공간이 부족한 경우에는 적재되어 있는 블록을 보조저장장치로 내보내고(swap-out), 새로운 블록을 읽어와서 그 공간에 적재(swap-in)

● 주기억장치와 보조저장장치 간의 속도 격차 증가

→보조저장장치의 성능 향상 필요

● 기계장치가 포함된 디스크 드라이브의 성능 한계

● SSD(Solid-State Drive) 출현

-비휘발성 반도체 기억장치들을 이용한 대용량 보조저장장치

(다수의 플래시 메모리들을 배열로 구성한 패키지)

-속도 및 신뢰도 향상

-디스크와는 다른 읽기/쓰기 특성을 가지기 때문에 별도 관리 필요

-상대적 고가 및 낮은 내구성(데이터 갱신 횟수 제한)

플래시 메모리

플래시 메모리의 출현 → 비휘발성 반도체 기억장치 분야 활성화 계기

● 높은 저장 밀도: 한 비트 저장에 한 개의 트랜지스터 사용

[비교] EEPROM: 비트 당 두 개의 트랜지스터 사용

● 낮은 전력소모량, 높은 신뢰성, 속도 향상

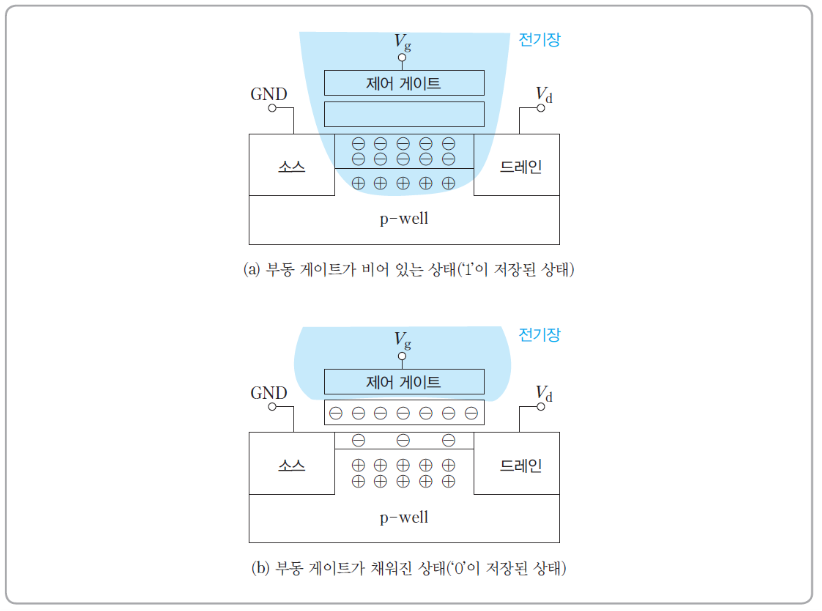

동작 원리

-메모리 셀(기억 소자) 구현: NMOS 트랜지스터 사용

-구조적 특징: 두 개의 게이트 (일반 NMOS는 한 개)

● 제어 게이트(control gate): 일반 트랜지스터의 게이트와 동일

● 부동 게이트(floating gate): 정보 저장의 핵심적 역할 수행

-메모리 셀의 기호 및 내부구조

- 부동 게이트 : 절연체인 산화막(SiO2)로 둘러싸여 전자들이 쉽게 들어오거나 나가지 못하며, 초기에는 비어있는(empty) 상태 = (‘1’ 저장 상태)

프로그래밍(쓰기) 동작: 제어 게이트로 고전압(예: +12V) 인가 시, 강력한 전기장 발생으로 N-채널의 전자들이 부동 게이트로 진입(터널링 효과로 인한 터널 주입 발생) ‘0’ 쓰기

-‘0’ 저장 : Vg = +12V 인가

-‘1’ 저장 : Vg = 0

삭제(erase) 동작: p층(p-well)에 고전압(Vp) 인가 시, 부동 게이트에 갇힌 전자들이 N-채널로 빠져 나옴 (터널 릴리스 현상)

-셀에 저장된 값 원래 값(‘1’)으로 변경

읽기 동작

-드레인 전압(Vd: 5V) 인가 N-채널을 통하여 전자 흐름 발생

-게이트 전압(Vg: 5V) 인가 전기장 발생

-저장된 데이터 = ‘1’ (부동 게이트가 빈 상태) 경우

- N-채널 확장 (그림 (a))

- 많은 전류가 흘러 트랜지스터가 ‘ON’ 상태 : ‘1’ 읽음

저장된 데이터 = ‘0’ (부동 게이트가 채워진 상태) 경우

- N-채널 유지 (그림 (b))

- 매우 적은 전류가 흘러 트랜지스터는 ‘OFF’ 상태 : ‘0’ 읽음

플래시 메모리의 셀 배열 조직

NOR형 플래시 메모리

메모리 셀 배열(memory cell array)이 NMOS 트랜지스터들의 병렬 접속으로 구성 (그림 (a)) : 전원(Vcc)이 비트 라인(BL)을 통하여 모든 트랜지스터들의 드레인으로 직접 공급되며, 트랜지스터들의 소스는 접지(GND)로 접속

→ 각 트랜지스터의 독립적 스위칭 동작 가능 (셀 단위 액세스 가능)

NOR형 플래시 메모리의 읽기 동작 원리

- ‘셀 배열의 트랜지스터(TR)에 ‘0’이 저장 된 상태에서 해당 단어 선(WL)으로 Vg=+5V 인가 : (TR: OFF) → BL = +5V 유지

-셀 배열의 어느 TR(들)에든 ‘1’이 저장 된 상태에서 Vg = +5V 인가 :

(TR: ON) → BL = 0V

-> “NOR 연산”

-(BL=0V) → 감지 증폭기(sensor amp)의 스위칭 동작에 의해, 최종 출력 = ‘1’, [(BL=+5V) → ‘0’ 출력]

-셀(비트) 단위 읽기 가능

NAND형 플래시 메모리

메모리 셀 배열이 NMOS 트랜지스터들의 직렬 접속으로 구성 (그림 (b)) : 전원(Vcc)이 첫 번째 트랜지스터의 드레인으로만 접속되고, 소스가 다음 트랜지스터의 드레인으로 접속되며, 마지막 트랜지스터의 소스만 접지

→ 트랜지스터의 독립적 스위칭 동작 불가능 (셀 단위 액세스 불가능)

NAND형 플래시 메모리의 읽기 동작 원리

-‘1’ 저장 상태에서, (TR: ON)을 위한 문턱 전압(threshold voltage: Vth) = -3V

-‘0’ 저장 상태에서는 Vth = +1V

-초기 상태: 모든 WL(Vg)=+5V (TR=ON)

-어느 한 셀의 읽기: 해당 Vg = 0V 인가

▶‘1’이 저장된 상태라면, Vg > Vth : (TR=ON) BL=0V [‘1’]

▶‘0’이 저장된 상태라면, Vg < Vth : (TR=OFF) BL=+5V [‘0’]

→ “NAND 연산”

-[최종 출력]은 센서증폭기에 의해 반전

NOR형 및 NADN형 플래시의 비교

NOR형

-셀(비트) 단위 읽기/쓰기 가능 : 프로그램 코드 저장, 작은 데이터 수시 인출 및 변경 응용에 적합

-셀 당 접속 선의 수 = 3개 낮은 저장 밀도(칩 당 저장용량 감소)

-주요 용도: PC-BIOS 저장장치, PDA/스마트폰 OS 저장장치, 등

NAND형

-셀(비트) 단위 읽기/쓰기 불가능 (페이지 단위만 가능)

-셀 당 접속 선의 수 = (2개)

→ 높은 저장 밀도 : 대용량 저장장치로 적합

-주요 용도: 백업 저장장치, SSD, 등

SLC, MLC 및 TLC

SLC(single-level cell): 두 가지 상태를 가짐으로써 한 비트를 저장하는 셀

MLC(multi-level cell): 셀의 상태를 4가지(00,01,10,11)로 구분 메모리 셀 당 2비트씩 저장

TLC(triple-level cell): 셀의 상태를 8가지(000, 001, 010, 011, 100, 101,110,111)로 구분 → 셀 당 3비트씩 저장

SSD(Solid-State Drive)

■ 기계적 장치가 포함된 하드 디스크 드라이브(HDD)를 대체하기 위해 개발된 대용량 비휘발성 반도체 저장장치

■ 구성요소: 저장밀도가 높은 NAND형 플래시 메모리

■ 다수의 플래시 메모리들을 배열로 구성하여 패키징

[장점]: 높은 안정성 및 신뢰도

[결점]: 저장용량 대비 가격이 HDD에 비해 다소 높음

SSD의 내부 조직

■ 플래시 메모리 칩

-PCB 앞면과 뒷면에 각각 4개의 64층 QLC 플래시 장착

-인터리빙 방식으로 데이터 분산 저장, 병렬 입출력 채널 구성

→ 동시 액세스 및 병렬 데이터 전송 지원

■ SSD 제어기(controller)

-데이터 저장과 인출, 칩 관리, 주소 변환 등과 같은 핵심적 기능 수행

-펌웨어 수준의 프로그램을 수행하는 프로세서로 구현

■ DRAM: 컴퓨터와 플래시 메모리 사이의 데이터 버퍼

-외부 인터페이스: SATA, PCIe 등을 이용한 직렬 전송

마모 평준화(wear leveling)

필요성

-플래시 메모리의 셀 수명(재기록 반복횟수: program/erase cycle)한계

-MLC 및 TLC에서 그 문제는 더욱 심각

-삭제 및 쓰기 동작들이 일부 블록이나 페이지들에 집중될 경우, 전체 SSD 수명 단축

해결책: 마모 평준화

-모든 페이지들이 고르게 사용되도록 저장 위치 조정

-각 페이지의 사용 횟수를 기록하여 쓰기 동작 시 참고

-기록 횟수가 적은 페이지 우선 사용

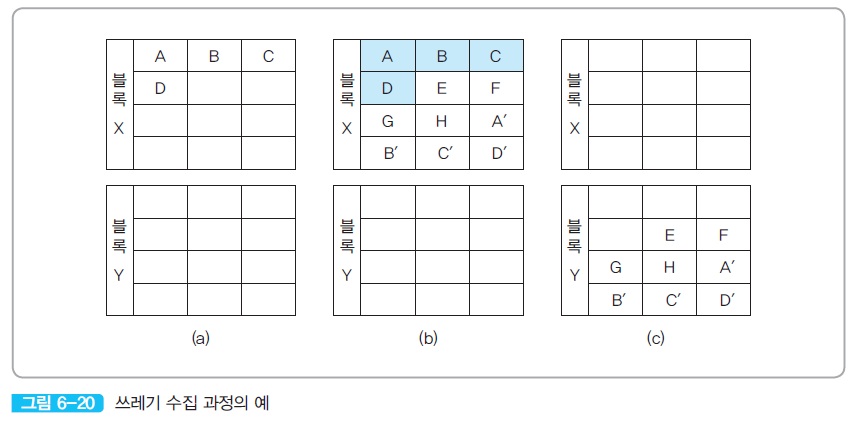

쓰레기 수집(garbage collection)

필요성

삭제 동작이 블록 단위로만 가능

페이지 수정 시, 마모 평준화 정책에 따라 다른 위치에 새로운 내용을 쓰고, 원래 페이지는 삭제 필요(페이지 단위는 삭제 불가)

해결책

페이지 내용은 수정되었지만 삭제하지 못한 원래 페이지는 쓰레기(garbage)로 표시

쓰레기로 표시된 페이지가 많이 축적된 블록을 한꺼번에 삭제: 쓰레기 수집 (삭제 전에 유효 페이지는 다른 블록으로 미리 이동)

쓰레기 수집의 예

ⓐ페이지 A, B, C, D가 블록 X에 저장된 상태

ⓑ새로운 페이지 E, F, G, H 저장하고,

기존 페이지들은 A’, B’, C’, D’로 수정하려 함

→덧쓰기(overwrite)가 되지않으므로, 다른 위치에 저장

→기존 페이지들은 무효 상태 : 쓰레기(garbage)

ⓒ블록 X에 있는 유효 페이지들을 다른 블록 Y로 이동(복사) 후,블록 X 전체를 삭제 = 쓰레기 수집 과정

TRIM 명령

-OS가 수행하는 명령으로서, SSD에게 무효 페이지들을 SSD 제어기에게 통보해줌으로써 쓰레기 수집의 효율을 높여 SSD의 성능을 향상시켜주는 보조 기능

-삭제 횟수를 최소화시켜주는 효과도 있음

초과 대비공간(over-provisioning: 오버-프로비저닝)

필요성

-마모 평준화의 효율을 높이기 위해서는 (수정된 페이지와 쓰레기 페이지의 일시적 중복 저장을 위한) 추가적 저장 공간 필요

해결책

-SSD 내부에 여분의 저장 공간 제공

사례

-Intel DC 3500 SSD : 120 GByte + 8 GByte(초과 대비공간)

-삼성전자 840 계열의 MZ-7TD250B SSD : 250 GByte +6 GByte(초과 대비공간)

'전공 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 시스템 버스 (0) | 2022.06.14 |

|---|---|

| [컴퓨터 구조] RAID(R3dundatn Array of Inexpensive Disk) (0) | 2022.06.13 |

| [컴퓨터 구조] 하드 디스크 (0) | 2022.06.13 |

| [컴퓨터 구조] DDR SDRAM (0) | 2022.06.12 |

| [컴퓨터 구조] 캐시 메모리(Chache Memory)(2) (0) | 2022.06.12 |

플래시 메모리와 SSD

주기억장치-보조저장장치 간 정보 전송의 필요성

● 시스템 초기화(부팅) 과정에서 OS 프로그램을 주기억장치로 적재

● 응용 프로그램이 처음 수행될 때는 디스크로부터 주기억장치로 적재

● 새로이 생성되거나 수정된 데이터는 보조저장장치에 영구 저장

● 주기억장치 공간이 부족한 경우에는 적재되어 있는 블록을 보조저장장치로 내보내고(swap-out), 새로운 블록을 읽어와서 그 공간에 적재(swap-in)

● 주기억장치와 보조저장장치 간의 속도 격차 증가

→보조저장장치의 성능 향상 필요

● 기계장치가 포함된 디스크 드라이브의 성능 한계

● SSD(Solid-State Drive) 출현

-비휘발성 반도체 기억장치들을 이용한 대용량 보조저장장치

(다수의 플래시 메모리들을 배열로 구성한 패키지)

-속도 및 신뢰도 향상

-디스크와는 다른 읽기/쓰기 특성을 가지기 때문에 별도 관리 필요

-상대적 고가 및 낮은 내구성(데이터 갱신 횟수 제한)

플래시 메모리

플래시 메모리의 출현 → 비휘발성 반도체 기억장치 분야 활성화 계기

● 높은 저장 밀도: 한 비트 저장에 한 개의 트랜지스터 사용

[비교] EEPROM: 비트 당 두 개의 트랜지스터 사용

● 낮은 전력소모량, 높은 신뢰성, 속도 향상

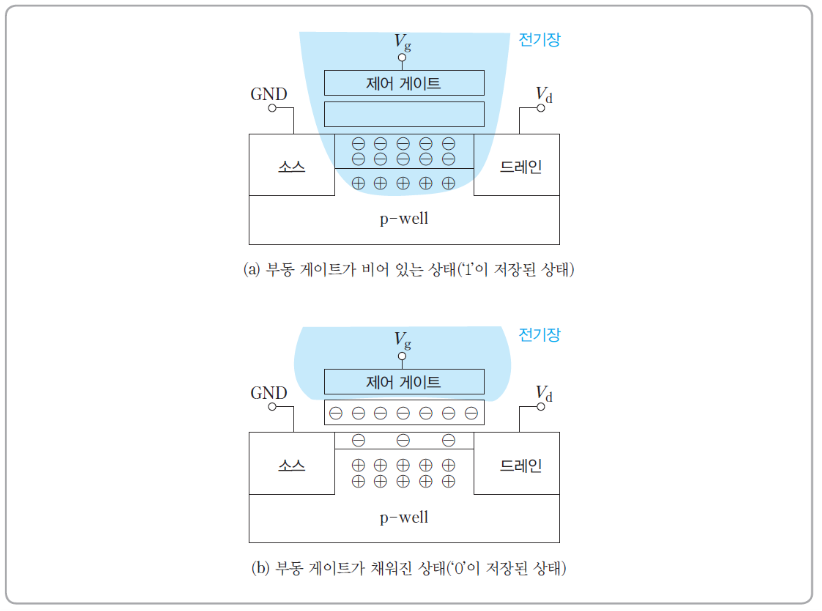

동작 원리

-메모리 셀(기억 소자) 구현: NMOS 트랜지스터 사용

-구조적 특징: 두 개의 게이트 (일반 NMOS는 한 개)

● 제어 게이트(control gate): 일반 트랜지스터의 게이트와 동일

● 부동 게이트(floating gate): 정보 저장의 핵심적 역할 수행

-메모리 셀의 기호 및 내부구조

- 부동 게이트 : 절연체인 산화막(SiO2)로 둘러싸여 전자들이 쉽게 들어오거나 나가지 못하며, 초기에는 비어있는(empty) 상태 = (‘1’ 저장 상태)

프로그래밍(쓰기) 동작: 제어 게이트로 고전압(예: +12V) 인가 시, 강력한 전기장 발생으로 N-채널의 전자들이 부동 게이트로 진입(터널링 효과로 인한 터널 주입 발생) ‘0’ 쓰기

-‘0’ 저장 : Vg = +12V 인가

-‘1’ 저장 : Vg = 0

삭제(erase) 동작: p층(p-well)에 고전압(Vp) 인가 시, 부동 게이트에 갇힌 전자들이 N-채널로 빠져 나옴 (터널 릴리스 현상)

-셀에 저장된 값 원래 값(‘1’)으로 변경

읽기 동작

-드레인 전압(Vd: 5V) 인가 N-채널을 통하여 전자 흐름 발생

-게이트 전압(Vg: 5V) 인가 전기장 발생

-저장된 데이터 = ‘1’ (부동 게이트가 빈 상태) 경우

- N-채널 확장 (그림 (a))

- 많은 전류가 흘러 트랜지스터가 ‘ON’ 상태 : ‘1’ 읽음

저장된 데이터 = ‘0’ (부동 게이트가 채워진 상태) 경우

- N-채널 유지 (그림 (b))

- 매우 적은 전류가 흘러 트랜지스터는 ‘OFF’ 상태 : ‘0’ 읽음

플래시 메모리의 셀 배열 조직

NOR형 플래시 메모리

메모리 셀 배열(memory cell array)이 NMOS 트랜지스터들의 병렬 접속으로 구성 (그림 (a)) : 전원(Vcc)이 비트 라인(BL)을 통하여 모든 트랜지스터들의 드레인으로 직접 공급되며, 트랜지스터들의 소스는 접지(GND)로 접속

→ 각 트랜지스터의 독립적 스위칭 동작 가능 (셀 단위 액세스 가능)

NOR형 플래시 메모리의 읽기 동작 원리

- ‘셀 배열의 트랜지스터(TR)에 ‘0’이 저장 된 상태에서 해당 단어 선(WL)으로 Vg=+5V 인가 : (TR: OFF) → BL = +5V 유지

-셀 배열의 어느 TR(들)에든 ‘1’이 저장 된 상태에서 Vg = +5V 인가 :

(TR: ON) → BL = 0V

-> “NOR 연산”

-(BL=0V) → 감지 증폭기(sensor amp)의 스위칭 동작에 의해, 최종 출력 = ‘1’, [(BL=+5V) → ‘0’ 출력]

-셀(비트) 단위 읽기 가능

NAND형 플래시 메모리

메모리 셀 배열이 NMOS 트랜지스터들의 직렬 접속으로 구성 (그림 (b)) : 전원(Vcc)이 첫 번째 트랜지스터의 드레인으로만 접속되고, 소스가 다음 트랜지스터의 드레인으로 접속되며, 마지막 트랜지스터의 소스만 접지

→ 트랜지스터의 독립적 스위칭 동작 불가능 (셀 단위 액세스 불가능)

NAND형 플래시 메모리의 읽기 동작 원리

-‘1’ 저장 상태에서, (TR: ON)을 위한 문턱 전압(threshold voltage: Vth) = -3V

-‘0’ 저장 상태에서는 Vth = +1V

-초기 상태: 모든 WL(Vg)=+5V (TR=ON)

-어느 한 셀의 읽기: 해당 Vg = 0V 인가

▶‘1’이 저장된 상태라면, Vg > Vth : (TR=ON) BL=0V [‘1’]

▶‘0’이 저장된 상태라면, Vg < Vth : (TR=OFF) BL=+5V [‘0’]

→ “NAND 연산”

-[최종 출력]은 센서증폭기에 의해 반전

NOR형 및 NADN형 플래시의 비교

NOR형

-셀(비트) 단위 읽기/쓰기 가능 : 프로그램 코드 저장, 작은 데이터 수시 인출 및 변경 응용에 적합

-셀 당 접속 선의 수 = 3개 낮은 저장 밀도(칩 당 저장용량 감소)

-주요 용도: PC-BIOS 저장장치, PDA/스마트폰 OS 저장장치, 등

NAND형

-셀(비트) 단위 읽기/쓰기 불가능 (페이지 단위만 가능)

-셀 당 접속 선의 수 = (2개)

→ 높은 저장 밀도 : 대용량 저장장치로 적합

-주요 용도: 백업 저장장치, SSD, 등

SLC, MLC 및 TLC

SLC(single-level cell): 두 가지 상태를 가짐으로써 한 비트를 저장하는 셀

MLC(multi-level cell): 셀의 상태를 4가지(00,01,10,11)로 구분 메모리 셀 당 2비트씩 저장

TLC(triple-level cell): 셀의 상태를 8가지(000, 001, 010, 011, 100, 101,110,111)로 구분 → 셀 당 3비트씩 저장

SSD(Solid-State Drive)

■ 기계적 장치가 포함된 하드 디스크 드라이브(HDD)를 대체하기 위해 개발된 대용량 비휘발성 반도체 저장장치

■ 구성요소: 저장밀도가 높은 NAND형 플래시 메모리

■ 다수의 플래시 메모리들을 배열로 구성하여 패키징

[장점]: 높은 안정성 및 신뢰도

[결점]: 저장용량 대비 가격이 HDD에 비해 다소 높음

SSD의 내부 조직

■ 플래시 메모리 칩

-PCB 앞면과 뒷면에 각각 4개의 64층 QLC 플래시 장착

-인터리빙 방식으로 데이터 분산 저장, 병렬 입출력 채널 구성

→ 동시 액세스 및 병렬 데이터 전송 지원

■ SSD 제어기(controller)

-데이터 저장과 인출, 칩 관리, 주소 변환 등과 같은 핵심적 기능 수행

-펌웨어 수준의 프로그램을 수행하는 프로세서로 구현

■ DRAM: 컴퓨터와 플래시 메모리 사이의 데이터 버퍼

-외부 인터페이스: SATA, PCIe 등을 이용한 직렬 전송

마모 평준화(wear leveling)

필요성

-플래시 메모리의 셀 수명(재기록 반복횟수: program/erase cycle)한계

-MLC 및 TLC에서 그 문제는 더욱 심각

-삭제 및 쓰기 동작들이 일부 블록이나 페이지들에 집중될 경우, 전체 SSD 수명 단축

해결책: 마모 평준화

-모든 페이지들이 고르게 사용되도록 저장 위치 조정

-각 페이지의 사용 횟수를 기록하여 쓰기 동작 시 참고

-기록 횟수가 적은 페이지 우선 사용

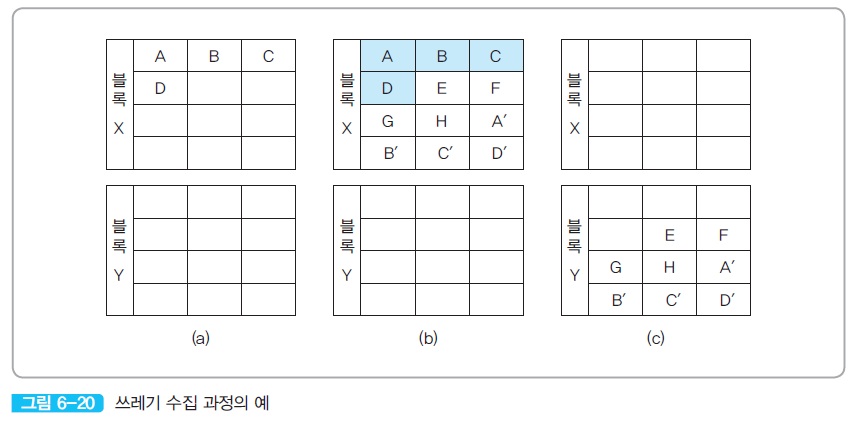

쓰레기 수집(garbage collection)

필요성

삭제 동작이 블록 단위로만 가능

페이지 수정 시, 마모 평준화 정책에 따라 다른 위치에 새로운 내용을 쓰고, 원래 페이지는 삭제 필요(페이지 단위는 삭제 불가)

해결책

페이지 내용은 수정되었지만 삭제하지 못한 원래 페이지는 쓰레기(garbage)로 표시

쓰레기로 표시된 페이지가 많이 축적된 블록을 한꺼번에 삭제: 쓰레기 수집 (삭제 전에 유효 페이지는 다른 블록으로 미리 이동)

쓰레기 수집의 예

ⓐ페이지 A, B, C, D가 블록 X에 저장된 상태

ⓑ새로운 페이지 E, F, G, H 저장하고,

기존 페이지들은 A’, B’, C’, D’로 수정하려 함

→덧쓰기(overwrite)가 되지않으므로, 다른 위치에 저장

→기존 페이지들은 무효 상태 : 쓰레기(garbage)

ⓒ블록 X에 있는 유효 페이지들을 다른 블록 Y로 이동(복사) 후,블록 X 전체를 삭제 = 쓰레기 수집 과정

TRIM 명령

-OS가 수행하는 명령으로서, SSD에게 무효 페이지들을 SSD 제어기에게 통보해줌으로써 쓰레기 수집의 효율을 높여 SSD의 성능을 향상시켜주는 보조 기능

-삭제 횟수를 최소화시켜주는 효과도 있음

초과 대비공간(over-provisioning: 오버-프로비저닝)

필요성

-마모 평준화의 효율을 높이기 위해서는 (수정된 페이지와 쓰레기 페이지의 일시적 중복 저장을 위한) 추가적 저장 공간 필요

해결책

-SSD 내부에 여분의 저장 공간 제공

사례

-Intel DC 3500 SSD : 120 GByte + 8 GByte(초과 대비공간)

-삼성전자 840 계열의 MZ-7TD250B SSD : 250 GByte +6 GByte(초과 대비공간)

'전공 > 컴퓨터 구조' 카테고리의 다른 글

| [컴퓨터 구조] 시스템 버스 (0) | 2022.06.14 |

|---|---|

| [컴퓨터 구조] RAID(R3dundatn Array of Inexpensive Disk) (0) | 2022.06.13 |

| [컴퓨터 구조] 하드 디스크 (0) | 2022.06.13 |

| [컴퓨터 구조] DDR SDRAM (0) | 2022.06.12 |

| [컴퓨터 구조] 캐시 메모리(Chache Memory)(2) (0) | 2022.06.12 |